弊社は半導体集積回路(IC)およびIC評価ボードのアナログ設計/測定業務を行っております.また,アナデジ混載LSIにおいて問題となる基板クロストーク雑音の解析・低減技術も保有しております.大学発ベンチャーの特色を活かして,新入社員やアナログ分野への入門者の方を対象にした人材育成やOJT,講習会も随時受け付けております.

アナログ回路設計

0.1um CMOSデバイスの遮断周波数(fT)は100GHzに達し,バイポーラデバイスより高速な動作が可能となります.これにより,CMOSチップ上に無線周波数(RF)回路を実現でき,CMOSアナログ回路との混載が可能となります.弊社では,CMOSアナ・デジ混載LSIに搭載するためのアナログ回路とRF回路の設計業務を行っています.

高性能アナログIP

弊社はADC/DACを中心とした種々の高精度/低消費電力のアナログIPを多数取り揃えております.保有IPをベースにして,お客様ご要望のプロセスに変換することも可能です.

高精度/低消費電力ASICの開発,アナログ要素回路の性能追求,チップ試作

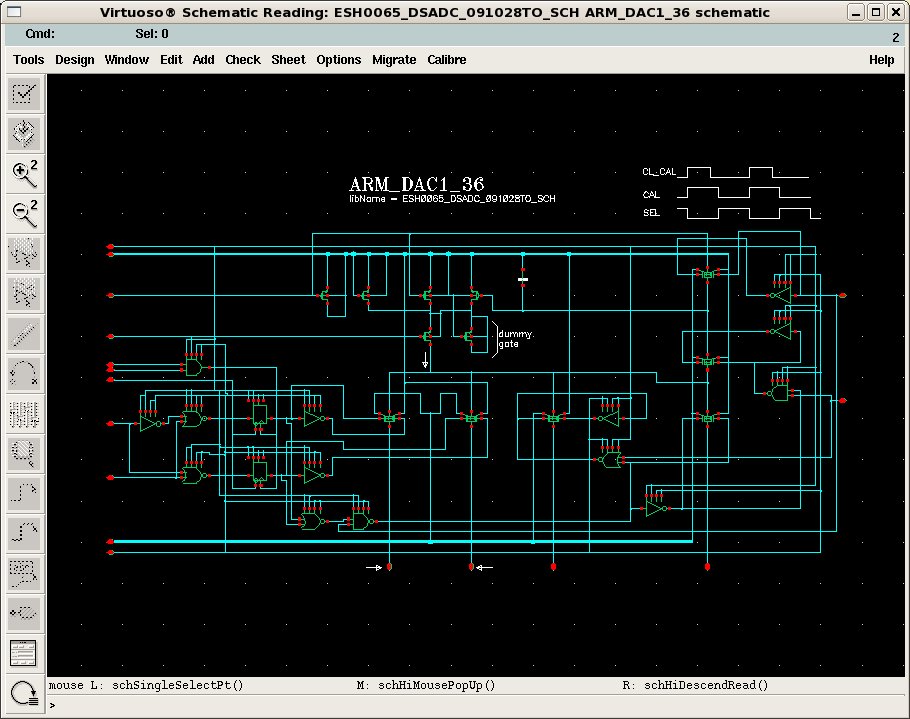

AD変換器

DA変換器

低雑音アンプ(Low Noise Amp: LNA)

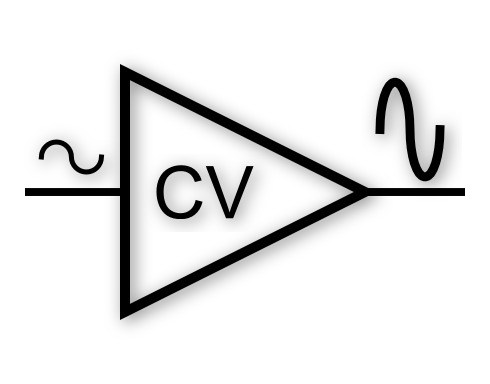

チャージアンプ(CV変換器)

低電源電圧オペアンプ

gm-Cフィルタ

バンドギャップ・リファレンス(BGR)

インタコネクション回路(チップ間)

電圧制御発振器(Voltage-Controlled Oscillator: VCO)

位相同期ループ(Phase Locked Loop: PLL)

RF回路

CMOSイメージセンサ

先端技術の調査研究,Feasibility Study

世界最先端技術の調査研究や,特定のIC製造プロセスを前提とした場合のFeasibility Study,限界性能の見極めなど幅広く承っております.

電子回路ボード(P板),モジュールの設計

設計したICのアナログ性能を引き出すための評価ボードおよびモジュールの設計を行っております.

以下は弊社で設計した評価ボード,モジュールの例です.

神経信号計測基板(16-ch電極実装)

音響センサー基板(32-ch入力)

脳埋め込み型 脳波検出モジュール(128-ch低雑音アンプ+ADC)

CCD信号処理ボード

CCDドライバボード

フレキ基板による生体信号検出モジュール

生体信号(皮質脳波:ECoG,神経活動電位:Spike)を検出するための電極です.フレキ材でできているため,柔軟に曲がります.フレキ材にはLCP(Liquid Crystal Polymer)を採用しており,耐水性が高く,生体適合性も良好です. くし形電極は脳に刺入して,Spike信号を検出します.1本当たり4個の電極を設けています. アレイ形電極は脳表面に接触させて,ECoG信号を検出します.電極数は8x8=64です. 市販のフレキ用コネクタによって,弊社で開発済みの信号処理モジュール(32/64-ch LNA+ADC)と接続することが可能です.

以下はフレキシブル基板を使って,電極と信号処理チップ(32/64-ch LNA+ADC)を一体型にしたモジュールです.電極からアンプまでの距離が長い場合,その経路で雑音が増えるのが問題になりますが,本モジュールではフレキシブル基板上に電極とチップが一体化されているため,そのような問題は最小限に抑えられます. 》生体情報センサーモジュールのパンフレット 》電極チップ一体型モジュールのカタログ

くし型電極チップ一体型モジュールの使用イメージ:

アナログ設計コンサルティング

各種アナログ設計に関するコンサルティング業務を承っております.

お気軽にこちらのフォームよりご相談ください.

アナログ回路の測定

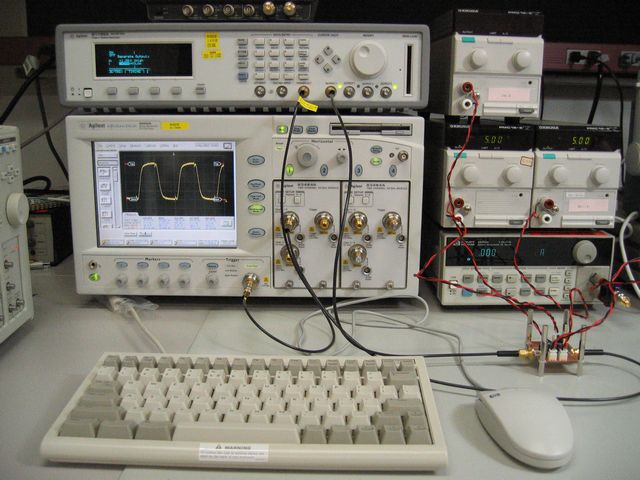

以下のようなアナログ回路の測定業務を承ります.

- ADC,DAC,AmpのDC/AC/Noise測定

- アナログ基本特性の評価

- 線形性の評価 - LNA,VCO,MIXのNF/Gain/PN/CG測定

- RF回路の諸特性の評価

- ネットワークアナライザによる利得,Sパラメータなどの評価 - CCD/CMOSセンサの測定,性能評価

- ダイナミックレンジの評価

- Noiseの評価 - トランジスタ単体のDC/AC/Noise測定

- 素子単体基本性能の評価

- 素子リーク電流の評価

- SPICEパラメータの精度検証 - 恒温槽による温特評価

- -40∼+150℃の温度特性の評価 - 自動測定系環境構築

- HP VEEを用いた自動測定系の環境構築

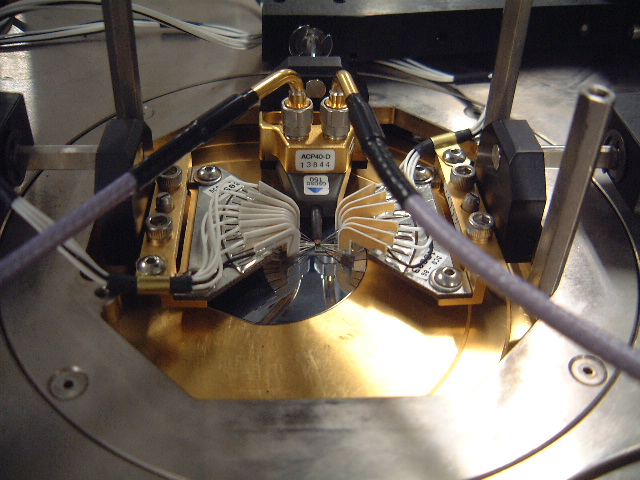

- 電源電圧/温度/レジスタ設定の自動スイープ - プローバによるオン・ウエハ測定

- 受動素子単体/トランジスタ単体のDC/AC/Noise測定

- RF回路のNF/Gain/Phase Noise/Conversion Gainの測定

基板雑音解析

アナデジ混載LSIの設計において,CMOSロジックの動作時に生じる過渡的電流変化と,それが基板伝播して起こる基板クロストーク雑音を如何に解決するかが重要な課題となっております.

弊社ではこれを解決してシグナル・インテグリティを達成するための技術として以下を提供しております.

測定,評価技術

モデリング,シミュレーション技術

基板雑音コンサルティング

アナログ回路単体では性能が出ているのに,デジタル回路と同時に動作させると,仕様が達成できなくなった経験はございませんか?

弊社は基板雑音の問題解決のスペシャリストです.高性能アナログ回路を含むアナデジ混載LSIの設計を予定されている方,あるいは既に製造が完了したLSIで,基板雑音でお困りの方,どうぞお気軽にこちらのフォームよりご相談ください.

基板雑音の発生メカニズムと回路モデル

フロアプラン雑音解析ツール(Floor Plan Noise Analysis:FPNA)

弊社では設計の初期段階で基板雑音に強いフロアプランを実現するための強力なツール(Floor Plan Noise Analysis:FPNA)を販売しております.

人材育成,OJT

アナログ・RF技術者の育成

近年,アナログ技術者の育成の要請は多く,要求条件は以下の例のように多岐にわたります.

- 電子回路が専門ではないので,基確知識から学びアナログ回路の設計ができるようになりたい.

- バイポーラトランジスタによるアナログ回路設計の経験を活かしてCMOSアナログ設計の専門家になりたい.

- 高周波,低電力,低雑音など高度なアナログ回路の設計ができるようになりたい.

- ニューラルネット,人工網膜など新しい回路の構成法や設計技術を身に付けたい.

この要請に,A-R-Tecではマンツーマンのオンザジョブで能力開発(OJT)を提案しています.

OJTのフロー

セミナーのような集合教育ではなく,OJTはマンツーマンで,研修内容・到達目標をカスタマイズできますので,真に有効な育成が可能になります.

- OJTの企画:企業の育成要請,受講者のレベル,希望に基づいて,指導者,指導場所,目標とするスキル,回路機能・性能およびスケジュールを相談して決める.

- OJTの実施:一定期間,指導場所に駐在して,Man to Manの指導を受けながら,回路シミュレータなどを使用して目標の回路を設計することにより設計技術を身に付ける.また,必要に応じてチップ試作・測定も行う.

受講者が自らの意思で頭をフル稼働させ手足を動かして実践できる環境を提供し,要所要所で適切な指導を行います.

日常業務から一定期間離れて,集中して能力開発に取り組むのです.普段とは異なる環境下で学ぶことでリフレッシュでき,好評です.

ご要望に応じて,弊社の共同研究大学(広島大学,神戸大学,中央大学,九州工業大学など)への受け入れも検討させていただいております.

アナログ・RF回路実習

1. アナログ回路設計実習

デルタシグマADCの基礎と機能Sim.

- 使用ツール(有償):MATLAB/Simulink,Verilog-A.

- 使用ツール(無償):Scilab/Scicos,Python/pylab.

要素回路(OPA, Comparator, Integrator,DAC)の回路設計.

- 使用ツール(有償):Spectre,HSPICE,SmartSpice.

- 使用ツール(無償):LTspice.

2. アナログ回路測定実習

OPA,DAC,ADCの諸特性を実測.カタログ項目を真に理解.

- 自動測定系(VEE),各種測定器を使用.

3. RF回路設計・測定実習

LNA,VCO,MIXの回路設計.

- 使用ツール(有償):Spectre(RF),HSPICE(RF),SmartSpice(RF),ADS.

- 使用ツール(無償):LTspice.

LNA,VCO,MIXの諸特性を実測.

- 自動測定系(VEE),各種測定器を使用.

4. A/D変換器基礎実習

A/D変換の基礎をSPICE-Simで理解.各種DAC,逐次比較ADCの回路設計.

- 使用ツール(有償):Spectre,HSPICE,SmartSpice.

- 使用ツール(無償):LTspice.

講習会

以下の内容で講習会を随時受け付けております. 基本的なアナログ回路の設計経験を有する方を対象に,実践的な内容を中心に解説致します.講師は実際のLSI設計に携わった弊社・技術者が親切・丁寧をモットーにして,受講者の方が理解できるまで徹底的に解説致します. 日程,開催場所はお客様のご要望に応じて調整させていただきます.